# PCI-4Pack-2 Custom for VEDA

Intelligent IP CARRIER for *PCI*<sup>™</sup> systems

Up to Four IndustryPack<sub>®</sub> Modules

Dual Ported SRAM between PCI and DSP C31

# **REFERENCE MANUAL**

736-21-000-4000 Version 2.1 August 1998

#### **ALPHI TECHNOLOGY CORPORATION**

6202 S. Maple Avenue #120 Tempe, AZ 85283 USA Tel: (602) 838-2428

Fax: (602) 838-4477

# **NOTICE**

The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, ALPHI TECHNOLOGY assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contain herein.

ALPHI TECHNOLOGY reserves the right to make any changes, without notice, to this or any of ALPHI TECHNOLOGY's products to improve reliability, performance, function or design.

ALPHI TECHNOLOGY does not assume any liability arising out of the application or use of any product or circuit described herein; nor does ALPHI TECHNOLOGY convey any license under its patent rights or the rights of others.

# ALPHI TECHNOLOGY CORPORATION All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted in advance.

# **TABLE OF CONTENTS**

| 1. GENERAL DESCRIPTION                    | 1  |

|-------------------------------------------|----|

| 1.1 INTRODUCTION                          |    |

| 1.2 FUNCTIONAL DESCRIPTION                | 1  |

| 1.3 REFERENCE MATERIALS LIST              | 3  |

| 2. HOST (PCI) SIDE                        | 4  |

| 2.1 PCI CONFIGURATION REGISTERS           |    |

| 2.2 PCI BASE ADDRESS REGISTERS            | 4  |

| 2.3 PCI OPERATION REGISTERS               |    |

| 3. C31 SIDE                               | 5  |

| 3.1 INTERNAL ORGANIZATION                 | 5  |

| 3.2 PCI INTERFACE                         | 5  |

| 3.3 DUAL PORT MEMORY                      | 6  |

| 3.4 IP INTERFACE and PAGED MEMORY         | 7  |

| 3.5 LOCAL MEMORY AND REGISTER MAP SUMMARY | 7  |

| 3.6 RESET SIGNALS                         | 10 |

| 3.7 LOCAL DSP INTERRUPT SOURCES           |    |

| 4. JUMPER DESCRIPTIONS                    | 11 |

| 5. LED INDICATORS                         | 12 |

| 6. CONNECTIONS                            |    |

| 6.1 IP I/O CONNECTORS                     |    |

| 6.2 SERIAL RS232 PORT (CON11)             | 13 |

| 6.3 SERIAL RS422 / RS485 PORT (CON2)      | 13 |

| 6.4 DSP SERIAL PORT (CON3)                |    |

| 6.5 EMULATOR CONNECTION (P16)             | 14 |

| 6.6 POWER FOR STAND ALONE OPERATION (P12) | 14 |

| 6.7 FACTORY USE (P15)                     | 14 |

| 7. STANDALONE OPERATION                   |    |

| 7.1 PCI RESET                             | 14 |

| 7.2 PCI BUS CLOCK                         | 14 |

#### 1. GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

The **PCI-4Pack** is a PCI expansion card in a standard full length form factor. The **PCI-4Pack** provides mechanical support and the electrical interfaces for four single width IP modules, or two double width IP modules. Multiple **PCI-4Pack** boards may be installed in a single system. The primary features of the **PCI-4Pack** are as follows:

- Support for up to four IP modules

- 8 MHz or 32 MHz IP operation via jumper selection

- On board DSP C31 to offload I/O operation from host or standalone applications

- Direct memory mapped access to the C31 from PCI bus via AMCC 5933 PCI Chip

- Direct dual ported memory access from PCI bus and C31 (up to 4 Mbytes)

- Full interrupt support of host and DSP C31

- Supports double-wide form factor IndustryPack®

- Front panel I/O connectors (for 2 IPs. Other 2 IPs require additional panel)

#### 1.2 FUNCTIONAL DESCRIPTION

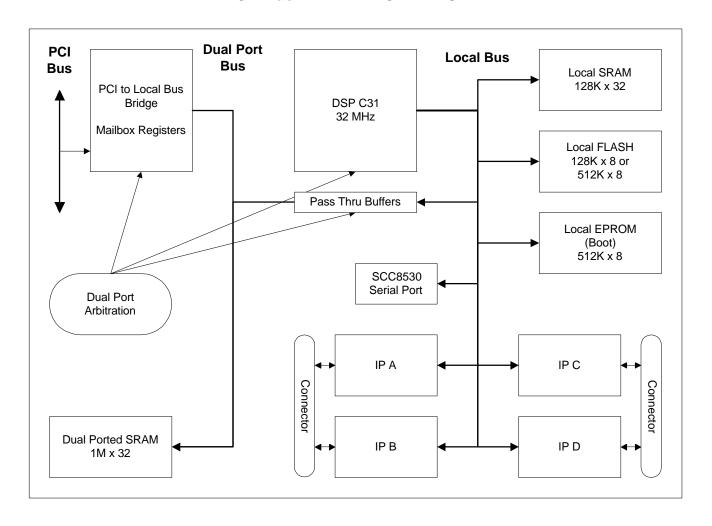

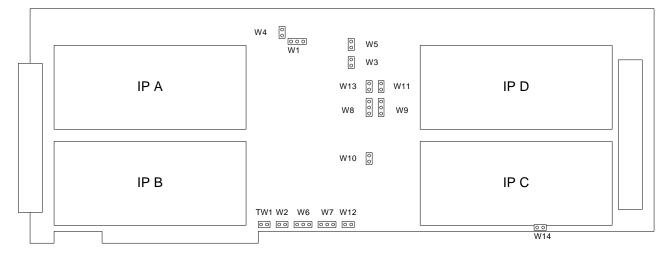

A functional block diagram of the **PCI-4Pack** is presented below in Figure 1-1. The component placement is depicted in Figure 1-2. The **PCI-4Pack** can operate as a slave that is managed by the host processor on the PCI bus or it can operate in a standalone mode of operation without a host. The IP modules share a common clock that can be jumpered for 8 or 32 MHz operation. Each pair of single width IPs, or each double width IP is individually selectable as to clock rate.

The **PCI-4Pack** is supported by ALPHI Technology under *Windows NT* by a **Board Support Package** which is supplied with the card. Other documentation supplied with the card will describe this support in full detail.

The card is also supported by a **DSP Support Library** providing the following features:

- Common access routines for communications with the host

- Mapping C language standard input and output by the DSP to the onboard 8530 serial chip

- Identify the applicable card resources and parameters

All these are provided in a manner consistent across ALPHI Technology platforms. Other documentation supplied with the card will describe the support in full detail.

A bootloader provided on the card allows for control by the HOST and for independent operation in stand alone operation. User code can be downloaded to FLASH memory and booted automatically on reset. Access to the card can be made both by the HOST PCI bus and serially through the 8530.

ALPHI TECHNOLOGY CORP. Page 1 Version 2.1

Figure 1.1: Block Diagram

Figure 1.2: Jumper Locations

ALPHI TECHNOLOGY CORP. Page 2 Version 2.1

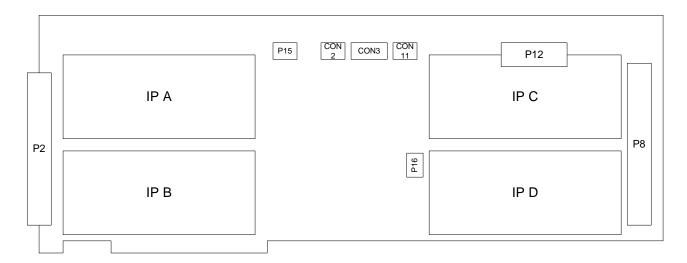

Figure 1.3: Connector Locations

#### 1.3 REFERENCE MATERIALS LIST

The reader should refer to the PCI Local Bus Specification for a detailed explanation of the PCI bus architecture and timing requirements. This specification is available from the following source:

PCI Special Interest Group

PO Box 14070

Portland, OR 97214 Tel: (800) 433-5177 Tel: (503) 797-4207 Fax: (503) 234-6762

The reader is also referred to the S5933 PCI Controller data book:

**AMCC Applied Micro Circuits Corporation**

6195 Lusk Boulevard

San Diego, CA 92121-2793

Tel: (800) 755-2622 http://www.amcc.com

WindowsNT and Windows95 Programming Tools:

**BlueWater Systems**

144 Railroad Ave. Suite #217

Edmonds, WA 98020 Tel: (206) 771-3610 Fax: (206) 771-2742

E-Mail: <a href="mailto:info@bluewatersystems.com">info@bluewatersystems.com</a> Web: <a href="mailto:http://www.bluewatersystems.com">http://www.bluewatersystems.com</a>

ALPHI TECHNOLOGY CORP. Page 3 Version 2.1

# 2. HOST (PCI) SIDE

#### 2.1 PCI CONFIGURATION REGISTERS

The card presents the following configuration values to the PCI system, based on the values stored in the NVRAM device read by the AMCC PCI interface chip.

| Register             | Value (Meaning)                                         |

|----------------------|---------------------------------------------------------|

| Vendor ID            | 0x13c5 (ALPHI Technology)                               |

| Device ID            | 0x0401 (PCI-4Pack)                                      |

| Revision ID          | 0x00                                                    |

| Class Code           | 0xff0000 (Device does not fit into defined class codes) |

| Interrupt Line       | 0xff                                                    |

| Interrupt Pin        | A                                                       |

| Multifunction Device | No                                                      |

| Build In Self Test   | No                                                      |

| Latency Timer        | 0x00                                                    |

| Minimum Grant        | 0x00                                                    |

| Maximum Latency      | 0x00                                                    |

| Expansion ROM Size   | None                                                    |

Table 2.1: PCI Configuration Registers

#### 2.2 PCI BASE ADDRESS REGISTERS

The card requests base address regions from the PCI system after RESET, based on the values stored in the NVRAM device read by the AMCC PCI interface chip.

The decode addresses of these regions are assigned by the host processor. The **PCI-4Pack** uses 3 of the 5 AMCC mapped base address registers. The AMCC is normally programmed at the factory to request the following resources from the PCI BIOS:

| BAR | From       | То         | Description                  | Туре |

|-----|------------|------------|------------------------------|------|

| 0   | 0x00000000 | 0x0000003F | AMCC PCI Operation Registers | MEM  |

| 1   | 0x00000000 | 0x00FFFFFF | Reserved for future use      | MEM  |

| 3   | 0x00000000 | 0x003FFFFF | Dual Port Memory             | MEM  |

| 3   | 0x00400000 | 0x01FFFFFF | Reserved for future use      | MEM  |

Table 2.2: Base Addresses and Use

NOTE: The AMCC has been programmed to request memory above 1 Mbytes.

#### 2.3 PCI OPERATION REGISTERS

The host processor communicates with the **PCI-4Pack** module via the AMCC pass-through interface. After the base address registers have been programmed by the PCI configurator, incoming PCI I/O or Memory cycles are translated into either accesses to the AMCC chip or

ALPHI TECHNOLOGY CORP. Page 4 Version 2.1

to the Dual Port SRAM. The PCI Operation Registers of the AMCC 5933 chip are depicted below:

| Offset | Register Name                            |

|--------|------------------------------------------|

| 0x00   | OMB1 Outgoing Mailbox Register 1         |

| 0x04   | OMB2 Outgoing Mailbox Register 2         |

| 80x0   | OMB3 Outgoing Mailbox Register 3         |

| 0x0C   | OMB4 Outgoing Mailbox Register 4         |

| 0x10   | IMB1 Incoming Mailbox Register 1         |

| 0x14   | IMB2 Incoming Mailbox Register 2         |

| 0x18   | IMB3 Incoming Mailbox Register 3         |

| 0x1C   | IMB4 Incoming Mailbox Register 4         |

| 0x20   | FIFO Register Port (bi-directional)      |

| 0x24   | MWAR Master Write Address Register       |

| 0x28   | MWTC Master Write Transfer Counter       |

| 0x2C   | MRAR Master Read Address Register        |

| 0x30   | MRTC Master Read Transfer Counter        |

| 0x34   | MBEF Mailbox Empty/Full Status           |

| 0x38   | INTCSR Interrupt Control/Status Register |

| 0x3C   | MCSR Bus Master Control/Status Register  |

Table 2.3: AMCC Registers (HOST)

For more information about these registers refer to the AMCC PCI controller manual.

# 3. **C31 SIDE**

#### 3.1 INTERNAL ORGANIZATION

The **PCI-4Pack** card is divided into different sections. Each section and its relationship to other sections will be discussed. The **PCI-4Pack** sections are:

- PCI interface

- Dual Port Memory

- IP interface

#### 3.2 PCI INTERFACE

The local DSP processor communicates with the PCI bus through the AMCCS9533 chip that provides bi-directional FIFO and Mailbox registers. The **PCI-4Pack** can function as both a servant (PCI target) or as a master (PCI initiator) for DMA access. The following interface descriptions refer to the PCI interface as seen by the local DSP. The AMCC registers are located at DSP address 0xf00080.

#### 3.2.1 BI-DIRECTIONAL FIFO

Two separate FIFO data paths are implemented within the AMCCS9533, a read FIFO that allows data transfers from the module to the PCI bus and a write FIFO that transfers data

ALPHI TECHNOLOGY CORP. Page 5 Version 2.1

from the PCI to the module. Size of the FIFO is 32 bit X 8. Read and write DMA access to the host can occur via the FIFO registers if it is supported by the software on the HOST and is enabled. Alternatively, the FIFO registers can utilize a polled scheme on the HOST and DSP. Both FIFOs are accessed via access to the same location as seen by the DSP, offset 0x08.

#### 3.2.2 MAILBOX REGISTERS

The Mailbox registers of the AMCCS9533 provide a bi-directional data path that can be used to send data or software control information between the HOST and the **PCI-4Pack** module. Interrupts can be enabled based on a specific mailbox event. There are 4 incoming mailboxes and 4 outgoing mailboxes. Each mailbox is 32 bits wide. The address offsets for the mailboxes are shown below in Table 3-1.

#### 3.2.3 ADDITIONAL REGISTERS

The AMCCS5933 PCI controller has a set of additional registers to control and monitor the behavior of the CPCI interface. Only the Add-on FIFO port is used by the **PCI-4Pack**.

The address offsets of these registers are shown below in Table 3-1.

| Offset | Register Name                          |

|--------|----------------------------------------|

| 0x00   | Incoming Mailbox Reg 1                 |

| 0x01   | Incoming Mailbox Reg 2                 |

| 0x02   | Incoming Mailbox Reg 3                 |

| 0x03   | Incoming Mailbox Reg 4                 |

| 0x04   | Outgoing Mailbox Reg 1                 |

| 0x05   | Outgoing Mailbox Reg 2                 |

| 0x06   | Outgoing Mailbox Reg 3                 |

| 0x07   | Outgoing Mailbox Reg 4                 |

| 80x0   | Add-on FIFO port                       |

| 0x09   | Bus master write Address Register      |

| 0x0A   | Add-on Pass through Address            |

| 0x0B   | Add-on Pass trough Data                |

| 0x0C   | Bus master read Address Register       |

| 0x0D   | Add-on Mailbox Empty/full Status       |

| 0x0E   | Add-on Interrupt Control               |

| 0x0F   | Add-on General Control/Status Register |

Table 3.1: AMCC Registers (DSP)

For more information about these registers refer to the AMCC PCI controller manual.

#### 3.3 DUAL PORT MEMORY

The dual port ram is directly accessed via memory writes and reads to locations in the range 00B00000h - 00BFFFFFh if 1 MWORD of memory is installed. This memory operates

ALPHI TECHNOLOGY CORP. Page 6 Version 2.1

at 3 or more wait states of the C31, with more when the HOST is accessing it as well. The HOST has priority during arbitration for a given cycle.

#### 3.4 IP INTERFACE and PAGED MEMORY

The ID and IO space for the IPs are directly accessed based on the memory map below. IP memory space is overlaid with the EPROM and FLASH space, and is controlled via CTRL 1.

#### 3.5 LOCAL MEMORY AND REGISTER MAP SUMMARY

| NAME      | START    | END      | DATA    | R/W | COMMENTS                   |

|-----------|----------|----------|---------|-----|----------------------------|

| SRAM      | \$000000 | \$01FFFF | D00-D31 | R/W | Zero wait state static RAM |

| EPROM     | \$400000 | \$47FFFF | D00-D07 | R/W | 512K x 8                   |

| FLASH     | \$480000 | \$49FFFF | D00-D07 | R/W | Software write protected   |

| IPMEMSL_A | \$400000 | \$7FFFFF | D00-D15 | R/W | IP_A memory ( 8 Mbytes )   |

| IPMEMSL_B | \$400000 | \$7FFFFF | D00-D15 | R/W | IP_B memory ( 8 Mbytes )   |

| IPMEMSL_C | \$400000 | \$7FFFFF | D00-D15 | R/W | IP_C memory ( 8 Mbytes )   |

| IPMEMSL_D | \$400000 | \$7FFFFF | D00-D15 | R/W | IP_D memory ( 8 Mbytes )   |

| DP_SRAM   | \$B00000 | \$BFFFFF | D00-D31 | R/W | Dual Port SRAM (4Mbytes)   |

| CTRL1     | \$F00000 | \$F00000 | D01-D03 | W   | Controls internal settings |

| CTRL2     | \$F00002 | \$F00002 | D01-D03 | W   | Controls internal settings |

| C31_STAT1 | \$F00008 | \$F00008 | D00-D07 | R   | IP interrupt status        |

| C31_STAT2 | \$F00009 | \$F00009 | D00-D07 | R   | IP DMA status              |

| C31_STAT3 | \$F0000A | \$F0000A | D00-D07 | R   | Miscellaneous status       |

| BERR_RST  | \$F00028 | \$F00028 | D00-D07 | W   | Reset Bus Error Status     |

| IPSTROBE  | \$F00038 | \$F00038 | D00-D31 | W   | Assert *IPSTROBE           |

| SCC8530   | \$F00040 | \$F00043 | D00-D07 | R/W | Serial communication port  |

| AMCC      | \$F00080 | \$F000FF | D00-D31 | R/W | AMCC REGISTERS             |

| IDSEL_A   | \$F00400 | \$F0043F | D00-D15 | R/W | IP_A ID Space              |

| INTGNT_A  | \$F00440 | \$F0047F | D00-D07 | R   | Interrupt vector from IP_A |

| IOSEL_A   | \$F00480 | \$F004BF | D00-D15 | R/W | IP_A I/O Space             |

| IDSEL_B   | \$F00500 | \$F0053F | D00-D15 | R/W | IP_B ID Space              |

| INTGNT_B  | \$F00540 | \$F0057F | D00-D07 | R   | Interrupt vector from IP_B |

| IOSEL_B   | \$F00580 | \$F005BF | D00-D15 | R/W | IP_B I/O Space             |

| IDSEL_C   | \$F00600 | \$F0063F | D00-D15 | R/W | IP_C ID Space              |

| INTGNT_C  | \$F00640 | \$F0067F | D00-D07 | R   | Interrupt vector from IP_C |

| IOSEL_C   | \$F00680 | \$F006BF | D00-D15 | R/W | IP_C I/O Space             |

| IDSEL_D   | \$F00700 | \$F0073F | D00-D15 | R/W | IP_D ID Space              |

| INTGNT_D  | \$F00740 | \$F0077F | D00-D07 | R   | Interrupt vector from IP_D |

| IOSEL_D   | \$F00780 | \$F007BF | D00-D15 | R/W | IP_D I/O Space             |

Table 3.2: DSP Memory Map

**ALPHI TECHNOLOGY CORP.** Page 7 Version 2.1

# 3.5.1 CTRL1 (Write Only)

| BIT 07 | BIT 06 | BIT 05 | BIT 04 | BIT 03   | BIT 02   | BIT 01   | BIT 00 |

|--------|--------|--------|--------|----------|----------|----------|--------|

|        |        |        |        | BANKSEL1 | BANKSEL0 | 32BIT_AB | FLASH  |

#### FLASH, BANKSELO, BANKSEL1

**Memory Page Selection**

The FLASH and EPROM, and the four IP memory spaces are all paged into a common DSP address range starting at 0x400000. Selection of the appropriate page is accomplished by programming the FLASH, BANKSEL0, and BANKSEL1 bits.

| CTRL1 | Page Selection            |

|-------|---------------------------|

| 0x0   | FLASH and EPROM (default) |

| 0x1   | IP_A Memory Space         |

| 0x5   | IP_B Memory Space         |

| 0x9   | IP_C Memory Space         |

| 0xD   | IP_D Memory Space         |

**Table 3-3: Memory Page Selection**

#### 32BIT\_AB 32-bit Width Enable

Setting this bit to a one enables the IP interface A and B for 32-bit transfers. Setting this bit to a zero disables the 32-bit transfers (default setting). This bit must be set to a one when using a double width IP. Note that the DSP always reads or writes in 32-bits, however only the lower 16 bits are valid when 32BIT\_AB = 0.

# 3.5.2 CTRL2 (Write Only)

| BIT 07 | BIT 06 | BIT 05 | BIT 04 | BIT 03    | BIT 02   | BIT 01   | BIT 00   |  |

|--------|--------|--------|--------|-----------|----------|----------|----------|--|

|        |        |        |        | EXTRIG_EN | CBERR_EN | 32BIT_CD | TCLK1_EN |  |

#### TCLK1 EN, EXTRIG EN

# Signal routing to IPSTROBE

See the following table for routing signals to \*IPSTROBE.

| TCLK1_EN, | EXTRIG_EN | Result                                                              |  |  |  |

|-----------|-----------|---------------------------------------------------------------------|--|--|--|

| 0         | 0         | Connect DSP Timer 1 output to *IPSTROBE                             |  |  |  |

| 1         | 0         | Software writes to register IPSTROBE (0xF00038) output to *IPSTROBE |  |  |  |

| Χ         | 1         | External TTL trigger on W13 output to *IPSTROBE                     |  |  |  |

#### 32BIT CD 32-bit Width Enable

Setting this bit to a one enables the IP interface C and D for 32-bit transfers. Setting this bit to a zero disables the 32-bit transfers (default setting). This bit must be set to a one when using a double width IP. Note that the DSP always reads or writes in 32-bits, however only the lower 16 bits are valid when 32BIT CD = 0.

#### CBERR EN Local Bus Error enable

Any access to a non-existent IP will never complete since no device will assert \*IPACK.

#### ALPHI TECHNOLOGY CORP.

To prevent this from happening, and hanging the DSP, any access to an IP also starts a timer to ensure that the cycle completes. The fact that this event occurs is reported in C31 STAT3, and can be cleared by writing to BERR RST.

If this bit is set, an IP interrupt is generated. Otherwise, no interrupt is generated.

# 3.5.3 C31\_STAT1 INTERRUPT STATUS REGISTER

| BIT 07 | BIT 06 | BIT 05 | BIT 04 | BIT 03 | BIT 02 | BIT 01 | BIT 00 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| IP_D   | IP_D   | IP_C   | IP_C   | IP_B   | IP_B   | IP_A   | IP_A   |

| IREQ1  | IREQ0  | IREQ1  | IREQ0  | IREQ1  | IREQ0  | IREQ1  | IREQ0  |

Each IP module can generate two different interrupts. When any Industry Pack generates an interrupt, the corresponding interrupt is ORed with other pending interrupts. The DSP can read this register to determine which interrupts are pending.

#### 3.5.4 C31\_STAT2 DMA STATUS REGISTER

|   | BIT 07 | BIT 06 | BIT 05 | BIT 04 | BIT 03 | BIT 02 | BIT 01 | BIT 00 |

|---|--------|--------|--------|--------|--------|--------|--------|--------|

| Ī | IP_D   | IP_D   | IP_C   | IP_C   | IP_B   | IP_B   | IP_A   | IP_A   |

|   | DMA1   | DMA0   | DMA1   | DMA0   | DMA1   | DMA0   | DMA1   | DMA0   |

The Industry Pack Specification allows for the possibility for an IP to request a DMA transfer. The **PCI-4Pack** does not directly support this option. However it is possible for the DSP to recognize a DMA request by polling the C31 STAT2 register. There is no interrupt support or direct DMA support by the DSP.

# 3.5.5 C31\_STAT3 MISCELLANEOUS STATUS REGISTER

| BIT 07 | BIT 06 | BIT 05 | BIT 04 | BIT 03 | BIT 02 | BIT 01 | BIT 00 |

|--------|--------|--------|--------|--------|--------|--------|--------|

|        |        |        |        |        | Jumper | Jumper | CBERR  |

|        |        |        |        |        | W3     | W5     |        |

# CBERR Bus Error Status

The DSP C31 can read this status register to know that a access to an IP has not responded by asserting \*IPACK. This status is reset with a write to BERR\_RST.

## JUMPER W3, W5 Status of Hardware Jumpers

These hardware jumpers are available for the use of the customer. If the jumper is installed, the bit reads as a 0.

#### 3.5.6 BERR\_RST

A write to this location will reset the CBERR bit in the C31\_STAT3 register.

#### 3.5.7 IPSTROBE

If the CTRL2 Register is configured to allow it, a write to this location will trigger a pulse on the \*IPSTROBE line to all the IPs.

**ALPHI TECHNOLOGY CORP.** Page 9 Version 2.1

#### 3.5.8 SERIAL PORT

The DSP processor on the PCI-4Pack has access to a SCC85C30 serial communication controller. The 8530 provides an RS232C asynchronous serial communication port and an RS422 port.

The bootloader and hardware support libraries supplied with the PCI-4Pack utilizes the RS232C port for a console for standard input and output by the DSP. The customer may alternatively wish to write his own software to use this port. Examples are provided in the **Board Support Package.**

There is hardware support for many RS422 and RS485 applications including HDLC, SDLC, and multidrop configurations. Clocking can be provided externally or internally.

#### 3.6 RESET SIGNALS

The **PCI-4Pack** can be reset from two different sources:

- At power on, the watchdog timer will hold the C31 RESET line and the IP reset lines low for 200 ms.

- The AMCC has a bit called SYSRST which the HOST can toggle to reset the DSP and IP resets. Software should hold the RESET asserted for 200 mS to meet the IP specifications

#### 3.7 LOCAL DSP INTERRUPT SOURCES

The local DSP has four interrupt lines. The source of each interrupt is listed in the table below. Additionally, at reset, the INT1 line is pulsed to tell the C31 to find the EPROM image at 0x400000 (if boot mode is MC).

| SOURCE       | ENABLE SIGNAL  | INTERRUPT LEVEL |

|--------------|----------------|-----------------|

| SCC8530      | Inside SCC8530 | INT0            |

| Bus Error    | CBERR_EN       | INT0            |

| AMCC         | Inside 5933    | INT1            |

| AMCC FIFO:   | None           | INT2            |

| WR not Full  |                |                 |

| RD not Empty |                |                 |

| IP interrupt | None           | INT3            |

Table 3-4

# 4. JUMPER DESCRIPTIONS

| JUMPER | FACTORY SETTING | DESCRIPTION                                                                                                                   |

|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| W1     | 1-2             | EPROM Addressing: 1-2 for 1 and 4 MB; 2-3 for 1 MB only.                                                                      |

| W2     | None            | If installed, forces PCI reset high for stand alone operation. Hosted operation is default.                                   |

| W3     | None            | Available to user for software configuration. The state is available in C31_STAT3.                                            |

| W4     | None            | Factory use only.                                                                                                             |

| W5     | None            | Available to user for software configuration. The state is available in C31_STAT3.                                            |

| W6     | 2-3             | IP A, B Clock Speed. 1-2 for 32 MHz, 2-3 for 8 MHz. 8 MHz is default.                                                         |

| W7     | 2-3             | IP C, D Clock Speed. 1-2 for 32 MHz, 2-3 for 8 MHz. 8 MHz is default.                                                         |

| W8     | 2-3             | Select input from RS422 pair 7 and 8. 1-2 to connect to receive clock of 8530; 2-3 to connect to CTS of 8530. CTS is default. |

| W9     | 2-3             | Select output to RS422 pair 4 and 5. 1-2 to output TXCLK generated by 8530. 2-3 to output RTS from the 8530. RTS is default.  |

| W10    | None            | DSP Boot Mode: MC/~MP. The card's boot mechanism is designed to operate in MC mode, booting from the EPROM.                   |

| W11    | None            | RS422 Driver Mode. If present, drive both outputs on RTS; otherwise drive always. Drive always is default.                    |

| W12    | None            | When shorted, provides DSP and IP reset.                                                                                      |

| W13    | None            | External trigger to generate *IPSTROBE pulse, if enabled in CTRL2 register.                                                   |

| W14    | 1-2             | Shorted when DSP operates at 32 MHz and OSC3 not installed; not when OSC3 installed for custom DSP frequency.                 |

| TW1    | None            | If installed, connects 32 MHz clock to PCI clock for stand alone operation and access to AMCC. Hosted operation is default.   |

**Table 4.1 Jumper Descriptions**

ALPHI TECHNOLOGY CORP. Page 11 Version 2.1

#### 5. LED INDICATORS

There are six LED indicators visible at the PCI card bracket. They are not marked with a legend on the bracket, but they are labeled on the PCB as L1 – L6 where L1 is at the top of the card.

The LEDs have the following meanings:

| LED | Meaning                                |

|-----|----------------------------------------|

| L1  | DSP is accessing IP D.                 |

| L2  | DSP is accessing IP C.                 |

| L3  | DSP is reading a register in the AMCC. |

| L4  | DSP is writing a register in the AMCC. |

| L5  | DSP is accessing IP B.                 |

| L6  | DSP is accessing IP A.                 |

Table 5.1 LED Descriptions

#### 6. CONNECTIONS

#### 6.1 IP I/O CONNECTORS

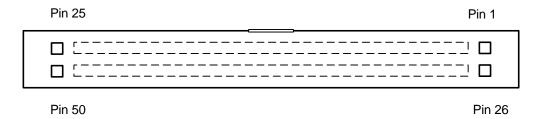

50 pin flat cable connectors are used to route all the IP I/O signals off the card. The mating connector reference is **HIROSE H1F6-50D-1.27R.** ALPHI Technology can supply transition modules and cable assemblies to meet any special requirements. Contact the factory for additional information.

Figure 6.1: IP I/O CONNECTORS

# 6.1.1 IP A (P2) and B (P3)

The I/O signals for IPs A and B are directly routed off the card through the front panel.

#### 6.1.2 IP C (P8) and D (P9)

The I/O signals for IPs C and D are placed such that they can only be accessed from inside the HOST chassis. ALPHI Technology has an optional panel and ribbon cable assembly which can be placed adjacent to the card to route these signals out of the HOST chassis.

ALPHI TECHNOLOGY CORP. Page 12 Version 2.1

# 6.2 SERIAL RS232 PORT (CON11)

Port A of the 8530 is configured as RS232 port, and it serves as the console output for the bootloader and any DSP programs linked with the ALPHI\_IO.LIB library discussed in the **DSP Support Library**. The pinout is described in the table below. An optional serial cable is available from the factory which connects to CON11 and terminates in a 9 PIN D, suitable for connection to a computer or terminal.

| Pin | Description     | Pin | Description   |

|-----|-----------------|-----|---------------|

| 1   | No Connection   | 2   | No Connection |

| 3   | Receive Data    | 4   | No Connection |

| 5   | Transmit Data   | 6   | No Connection |

| 7   | Clear To Send   | 8   | No Connection |

| 9   | Request To Send | 10  | No Connection |

Table 6.1: Serial RS232 Port (CON11)

# 6.3 SERIAL RS422 / RS485 PORT (CON2)

Port B of the 8530 is configured as a combination RS422 / RS485 port. The port can be configured to communicate with many other devices in a dedicated direct link as well as a multidrop link, depending on jumper settings. The pinout is described in the table below.

| Pin | Direction | Description      | Pin | Direction | Description      |

|-----|-----------|------------------|-----|-----------|------------------|

| 1   | Output    | Transmit Data +  | 2   | Output    | Transmit Data -  |

| 3   | Input     | Receive Data +   | 4   | Output    | RTS + or TXCLK + |

| 5   | Output    | RTS – or TXCLK - | 6   | Input     | Receive Data -   |

| 7   | Input     | CTS + or RXCLK + | 8   | Input     | CTS - or RXCLK - |

Table 6.2: Serial RS422 / RS485 Port (CON2)

#### 6.4 DSP SERIAL PORT (CON3)

The serial shift register of the DSP is also available for use as desired by the customer. The input and outputs are connected to 55194 and 55195 bipolar line drivers and receivers as shown in the following table. See the DSP Processor manual for details on how to use the serial port.

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | FSR0 -      | 2   | FSX0 +      |

| 3   | FSR0 +      | 4   | FSX0 -      |

| 5   | Ground      | 6   | Ground      |

| 7   | DR0 -       | 8   | DX0 +       |

| 9   | DR0 +       | 10  | DX0 -       |

| 11  | Ground      | 12  | Ground      |

| 13  | CLKR0 -     | 14  | CLKX0 +     |

| 15  | CLKR0 +     | 16  | CLKX0 -     |

Table 6.3: DSP Serial Port (CON3)

ALPHI TECHNOLOGY CORP. Page 13 Version 2.1

# 6.5 EMULATOR CONNECTION (P16)

This connector is used to connect the emulator to the C31 DSP. It follows the standard form as described by TI in their processor manual.

# 6.6 POWER FOR STAND ALONE OPERATION (P12)

When the board is operating in stand alone mode, this connector can be used in place of the PCI connector to supply power to the card and IPs. The card requires +5 volts; the +12 and -12 volts are only necessary if the installed IPs require it.

| Pin | Use       |  |

|-----|-----------|--|

| 1   | +5 Volts  |  |

| 2   | Ground    |  |

| 3   | +12 Volts |  |

| 4   | Ground    |  |

| 5   | -12 Volts |  |

Table 6.4: Power for Stand Alone Operation (P12)

# 6.7 FACTORY USE (P15)

This connector is used at the factory for programming the FPGA.

#### 7. STANDALONE OPERATION

When the board is operated without a PCI HOST, two signals must be driven in order to assure correct operation. These signals are provided by placing the correct jumpers on the board when in stand alone operation. If the board is returned to a PCI hosted environment, these jumpers must be removed, or they will interfere with the correct operation of the PCI host.

When the board is operated in stand alone mode, the board can by operated under an emulator and by downloading and executing programs via the serial port under control of the bootloader.

#### 7.1 PCI RESET

This signal must be pulled high by inserting a jumper in location xx for stand alone operation. In a hosted environment, it must be removed.

# 7.2 PCI BUS CLOCK

The AMCC requires that a PCI BUS clock be present for its internal operation. This signal must be driven by the internal clock oscillator when operated in stand alone operation. This is accomplished by inserting a jumper in location xx for stand alone operation. In a hosted environment, it must be removed.

ALPHI TECHNOLOGY CORP. Page 14 Version 2.1